Prof. Manuel Jimenez – Advisor

University of Puerto Rico,

## ALSAIP

Rafael Arce-Nazario – Ph.D. Student AIP Group, CISE Program, Email: rafael.arce@ece.uprm.edu

## Abstract

High-level partitioning (HLP) is an essential step in the implementation of algorithms to distributed hardware architectures (DHA), such as multi-FPGA platforms. Fast discrete signal transform algorithms (e.g. FFT, FCT) have a number of decomposition and reformulation properties that offer opportunities for developing semantically guided high-level partitioning schemes that influence their mapping to hardware. Based on this hypothesis, we are conducting research to devise a functionally-aware methodology that uses these types of transformations to provide improved results for the high-level partitioning of discrete signal transforms to DHAs.

## Motivation and Objectives

Discrete Signal Transforms (DSTs): major component in today's applications

- DST partition is of interest because:

- high logic resource utilization Multi-FPGA / Reconfig. Comp.

- trend toward multi-core/SoC

• Previous automated schemes treat DSTs in generic way.

•DSTs have properties that can be used to aid High Level partitioning

- fast algorithms: regularity, factorization rules, recursiveness

- compact, systematic manipulation at the algorithmic level using Kronecker Products Algebra (KPA).

Hypothesis: Improve DST to multi-FPGA partitioning process by considering DST properties and reformulation.

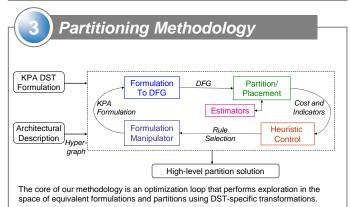

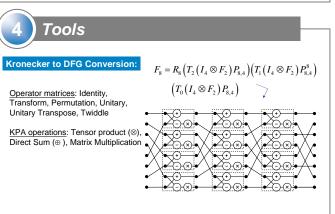

- 1. <u>Kronecker to graph (KTG) conversion</u> generates DFG corresponding to (KPA) formulation. Each DFG node is a primitive from the formulation.

- A <u>Partitioning/placement (P/P)</u> algorithm is run on the DFG, which consults <u>Area/Communication estimators</u> to determine current solution's quality.

- Indicators output by <u>Partitioning/placement (P/P)</u> are used by a <u>Heuristic Control</u> to chose rule for reformulation, which is performed by the <u>Formulation Manipulator</u>.

- 4. Process is iterated until no further significant gain is being achieved.

www.walsaip.uprm.edu

## Ongoing Work and Conclusions

The introduction of DST considerations into the graph partitioning heuristics, as well as the algorithmic-level exploration of DSTs, help our methodology obtain improved partitioning results in considerably less time than general purpose partitioning methods.

Currently, the proposed partitioning methodology is being extended to work with discrete cosine transforms (DCT). The extension required development of a Cooley Tukey-like factorization scheme for DCTs, and generated improved results over other existing regular DCT formulations.

8 References

UPR

R. Arce-Nazario, M. Jimenez, and D. Rodriguez. "Functionally-aware Partitioning of Discrete Signal Transforms for Distributed Hardware Architectures". 49th Midwest Symposium on Circuits and Systems. August 2006. San Juan, Puerto Rico.

R. Arce-Nazario, M. Jimenez, and D. Rodriguez. "High-level Partitioning of Discrete Signal Transforms for Multi-FPGA Architectures". IEEE 16th International Conference on Field Programmable Logic and Applications. August 2006. Madrid, Spain.

ALSAIP

Supported By

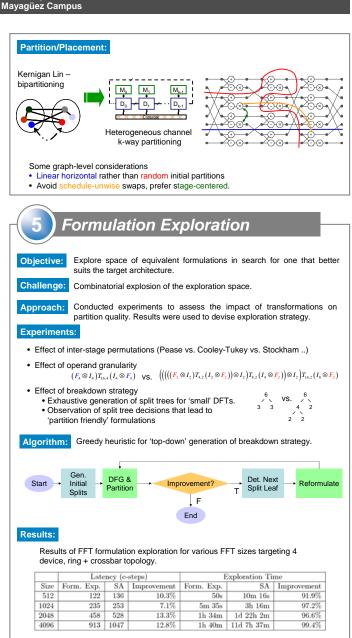

**RAN1** Fromulation exploration

-> can lead to exponential

explosion

-> mention experiments: perm,

gran, split trees

-> observation on split trees,

etc..

-> algorithm

-> results

-> references: MWSCAS06, FPL

-> ongoing work.. Rafa, 1/23/2007